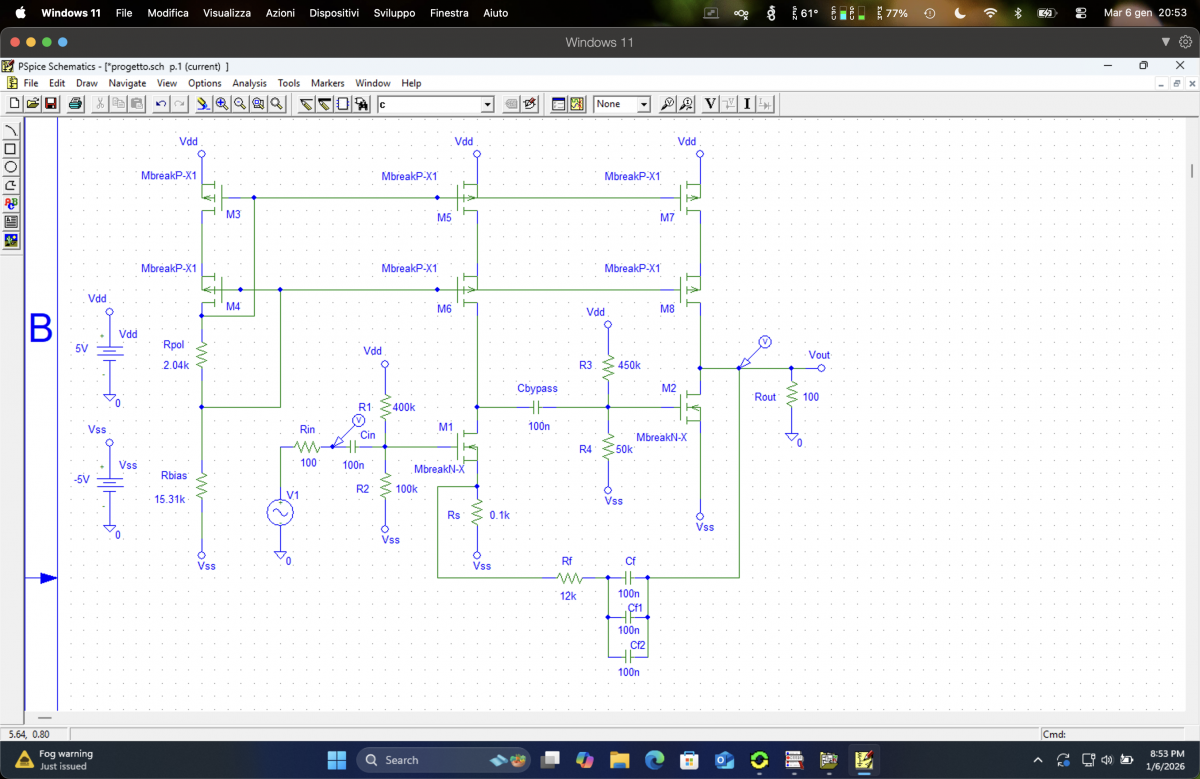

Di seguito lo schematico del mio primo progettino di elettronica

Questo progetto è stato creato da me assieme a dei miei colleghi durante il corso di Elettronica Analogica frequentato al Politecnico di Milano, lo schematico è di un circuito integrato amplificatore pensato per amplificare il suono di un microfono con bassa distorsione, di seguito la consegna del lavoro assegnata:

" Un sistema audio è dotato di un microfono che produce un segnale in tensione proporzionale al suono che esso riceve in entrata. Il microfono si può modellare come un generatore di segnale la cui ampiezza varia nell’intervallo 1mV÷10mV e la cui frequenza varia tra 1kHz e 8kHz, con una resistenza serie di 100Ω. A valle del sistema audio è presente uno speaker, che deve essere pilotato con una distorsione inferiore allo 0.3%, al fine di generare un suono non distorto. Lo speaker ha un’impedenza d’ingresso pari a 100Ω. Si progetti l’amplificatore da porre tra microfono e speaker.

L’amplificatore dovrà avere quindi le seguenti caratteristiche:

- Alimentazione: +/- 5V

- THD massima: 0.3%

- Massima potenza dissipata dal circuito: 500mW

- Variazione minima di tensione ai capi dello speaker: 100mV

- Capacità massima utilizzabile: 100nF

Caratteristiche dei MOS:

- 𝜇n𝐶ox' = 70 𝜇A/𝑉2

- 𝜇p𝐶ox' = 200 𝜇A/𝑉2

- Lmin = 0.25 𝜇m

- Vt = 0.5V

- VA = 50 V (𝜆 = 0.02 V-1)

Non possono essere usati generatori di corrente di polarizzazione ideali, ma devono essererealizzati con transistori. "

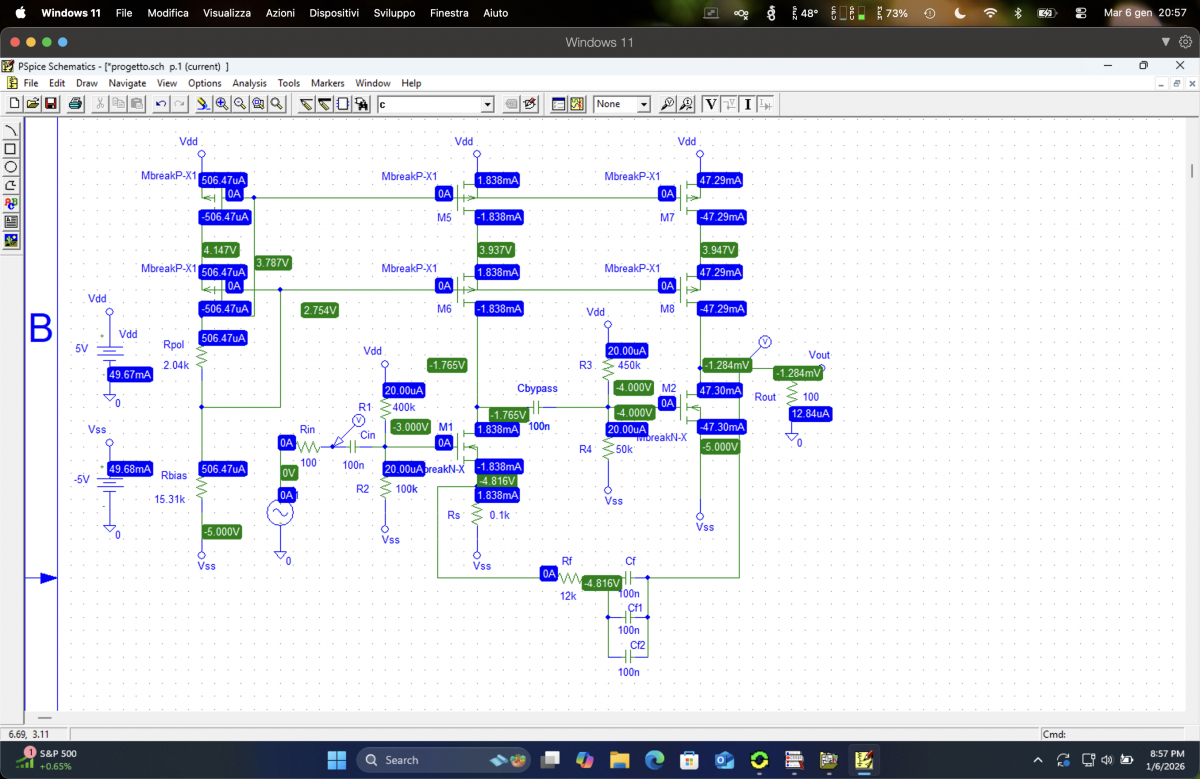

Di seguito, risparmiandovi i conti aggiungo lo schematico simulato completo di polarizzazione, la prima sfida infatti ha riguardato proprio quest'ultima per polarizzare correttamente i transistori in modo da rispettare la dinamica di ingresso/uscita e rientrare nei limiti di potenza statica consumata, a questo scopo sono state inserite delle capacità disaccoppiatrici all'ingresso del segnale e tra i due stadi amplificanti con capacità e resistenze di polarizzazione abbastanza elevate da abbassare i poli da essi introdotti a frequenze maggiori di quelle del segnale (8 kHz).

L'altra sifda imponente è stat quella di ridurre la distorsione, a questo scopo abbiamo fatto in modo che il guadagno fosse composto da due stadi invertenti, in primis per ottenere un segnale non invertito e anche per ridurre la distorsione, infatti sommandosi le distorsioni introdotte dai due nMos esse tendono a compensarsi. L'utilizzo del doppio specchio di corrente è al fine di massimizzare l'impedenza di uscita dei generatori di corrente presenti nel circuito. Come è possibile intuire dallo schematico, il guadagno del secondo stadio è minore del primo poichè per poter pilotare un carico con impedenza così bassa si deve avere un'uscita in corrente. I valori dei k sono i seguenti:

M1 kn = 1 mA/𝑉2; M2 kn = 172 mA/𝑉2; M3-M4 kp = 980 𝜇A/𝑉2; M5-M6 kp = 1.76 mA/𝑉2; M7-M8 kp = 86.1 mA/𝑉2.

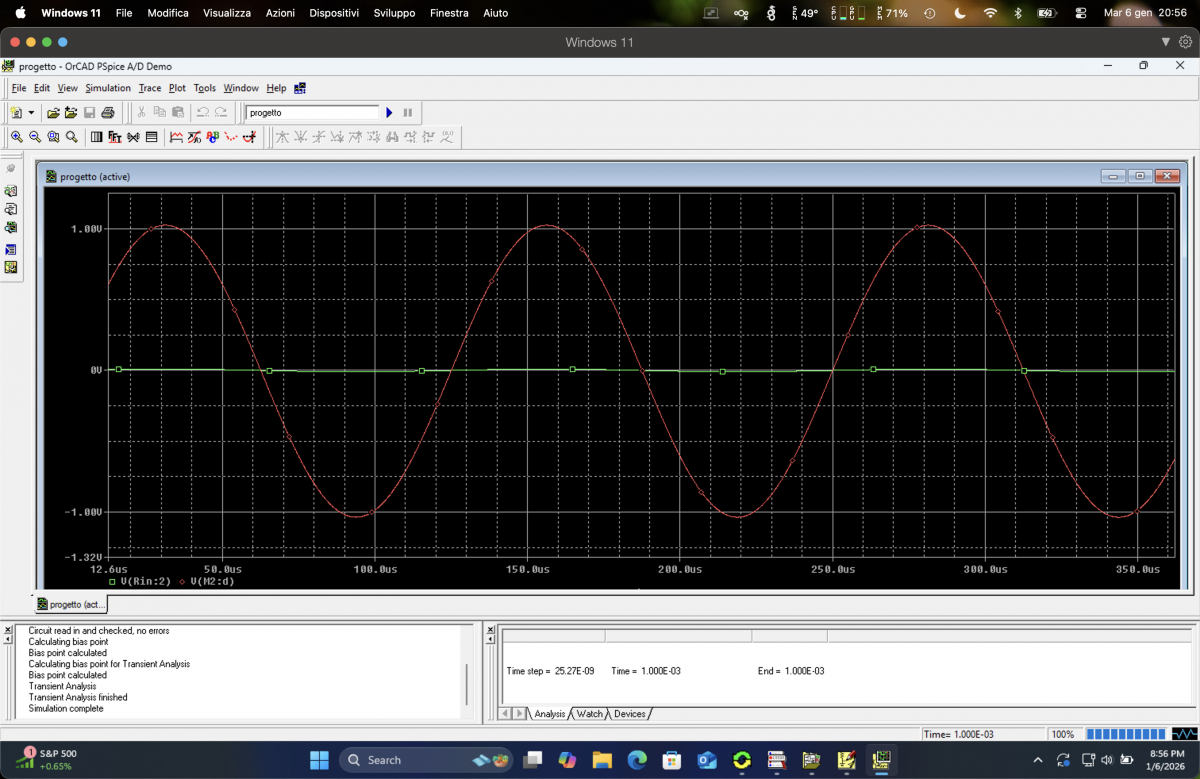

Così facendo l'amplificatore ha un'amplificazione maggiore di 400, al fine di abbassare ancor di più la distorsione possiamo "erodere" un po' di questo guadagno (non necessario oltre i 100) per migliorare la stabilità, retroazionando negativamente il circuito. Per evitare problemi sulla polarizzazione e la dinamica poniamo in serie alla resistenza di retroazione una capacità che per mantenere la distorsione sotto gli 0.3% nel caso peggiore ovvero ad 1 kHz e 10 mV deve essere del valore minimo di 300 nF che sfora la richiesta iniziale di massimo 100nF, lo stratagemma da noi utilizzato è stato di mettere 3 capacità in serie un po' barando, in realtà sarebbe possibile diminuire di qualche mV il comando del secondo transistor per diminuire di quanto basta la distorsione per rientrare nei valori di distorsione desiderati con una Cf = 100nF. Già questo circuito con una sola Cf = 100nF in casi di frequenza maggiore di 1 kHz a parità di ampiezza o di ampiezze minori di 10 mV a parità di frequenza soddisfa tutti i criteri.

Questo primo progetto è stato molto interessante e critico in alcuni suoi momenti di creazione, ma fondamentale per la comprensione della creazione di circuiti integrati elettronici.

01/06/2026 21:32:32